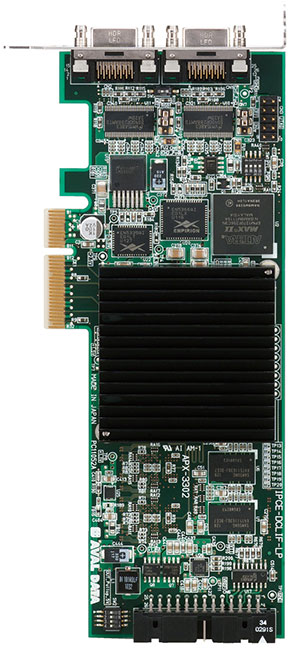

APX-3307-260

CL Base x 2Ch, FPGA 处理卡

| 型号 | APX-3307-260 |

| 输入图像/td> | CameraLink Base Configuration 2ch 两个SDR接口 采样时钟85MHz (MAX) 图像数据颜色(RGB) : 24bit, 黑白: 8(1/2/3Tap), 10, 12bit (1/2Tap) |

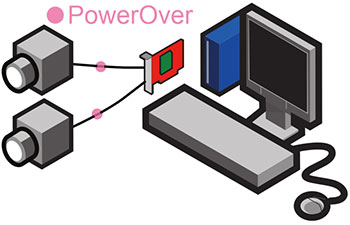

| PoCL | 对应 |

| MEGA-FIFO | DDR2-SDRAM 128MB |

| 内存 | 387MB |

| FPGA | ALTERA EP2AGX260 (用户可以通过FPGA开发图像处理) |

| 同步输出 | 像机控制信号: CC1~CC4 通用输出: 2ch 异步 TTL / Open collector (以Strobe timing输出) |

| 同步输入 | 外部触发器: TTL / Open collector / 差分信号 RS-422 编码器: 差分信号 RS-422 (线路驱动器), A / B / Z 相, 1MHz (MAX) 通用输入: TTL / Open collector |

| 中断 | 开始图像输入, DMA end, GPIN 等 |

| 系统 Bus | PCI Express 2.0 x4 (Gen2) 2.5GT / S |

| 电源 | + 12V |

| 使用环境 | 0 ℃ ~ 50 ℃, 湿度: 35 % ~ 85 % (无结露) |

| 外形尺寸 | Low Profile 167.65mm × 68.9mm 面板幅度 20mm (除突出部) |

| OS | Windows 10 / 7 对应各 32bit / 64bit, Linux |

| 软件(可选) | SDK : SDK-AcapLib2 FDK : AZP-FDK APX-3307 |

注意

– 规格和外观如有变更,恕不另行通知。

– 电源不包括浪涌电流。

– 为正确使用本产品,请在使用前阅读使用说明书,请在产品保修范围内使用。

ENG

ENG KOR

KOR CHN

CHN JPN

JPN