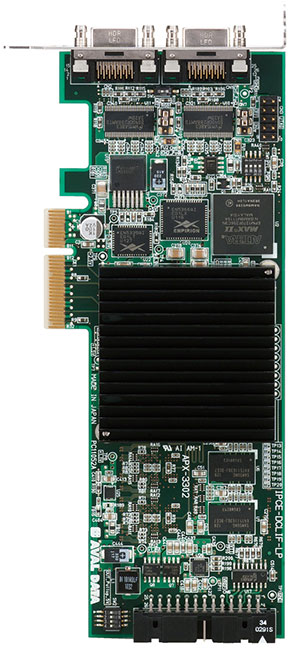

APX-3307-260

CL Base x 2Ch, FPGA처리 보드

| 모델명 | APX-3307-260 |

| 이미지 입력 I / F | CameraLink Base Configuration 2ch SDR커넥터 2개 탑재 샘플링 클럭 85MHz (MAX) 이미지 데이터 컬러(RGB) : 24bit, 모노: 8(1/2/3Tap), 10, 12bit (1/2Tap) |

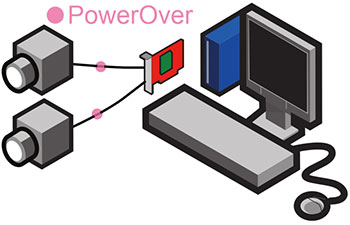

| PoCL | 지원 |

| MEGA-FIFO | DDR2-SDRAM 128MB |

| 메모리 | 387MB |

| FPGA | ALTERA EP2AGX260 (FPGA를 통한 이미지처리를 사용자가 개발 가능) |

| 동기회 출력 | 카메라 제어 신호: CC1~CC4 범용 출력: 2ch 비동기 TTL / 오픈 콜렉터 (Strobe timing출력으로도 가능) |

| 동기화 입력 | 외부 트리거: TTL / 오픈 콜렉터 / 차동 신호 RS-422 인코더: 차동 신호 RS-422 (라인 드라이버), A / B / Z 상, 1MHz (MAX) 범용 입력: TTL / 오픈 콜렉터 |

| Interrupt | 이미지 입력 시작, DMA end, GPIN 등 |

| 시스템 Bus | PCI Express 2.0 x4 (Gen2) 2.5GT / S |

| 전원 | + 12V |

| 사용 환경 | 0 ℃ ~ 50 ℃, 습도: 35 % ~ 85 % (무결로) |

| 외형 치수 | Low Profile 167.65mm × 68.9mm 패널 폭 20mm (돌출부 제외) |

| OS | Windows 10 / 7 각 32bit / 64bit에 대응, Linux |

| 소프트웨어 (옵션) | SDK : SDK-AcapLib2 FDK : AZP-FDK APX-3307 |

참고 : 기재된 사양 및 외관은 예고없이 변경되는 경우가 있습니다.

– 전원은 돌입 전류를 포함하고 있지 않습니다.

– 올바른 제품 사용을 위해 사용 전에 반드시 사용 설명서를 읽고 제품 보증 범위 내에서 사용하십시오.

ENG

ENG KOR

KOR CHN

CHN JPN

JPN