APX-5040

14 bit/400 MHz high speed sampling A/D conversion Board

| Item | Specification |

| Model name | APX-5040 |

| Input channel | Single end 2ch |

| Sampling clock | 400MHz |

| Resolution | 14bit |

| Sampling time | 2.5ns(min) |

| Number of samples | 256 M words / 1 channel |

| Input range | ±2V±1V±500mV |

| Input impedance | 50Ω |

| Trigger | External trigger / Analog trigger / Soft trigger / DI trigger (Various trigger modes supported by FPGA) |

| Memory | DDR3 – SDRAM (2 GB) |

| FPGA | LSI: EP4SGX180HF35C2N (manufactured by ALTERA) Trigger type: Internal trigger (analog trigger), external trigger, soft trigger, DI trigger Analog trigger: Edge level pulse Trigger position: pre / post delay User logic: Free space can be customized |

| External Clock | Input(PPL) : 5MHz, 100MHz Input(Direct input) : 500MHz, 1000MHz |

| DA Circuit | Number of outputs: 2 ch Resolution: 16 bits Output range: -4 V to +4 V |

| System bus | PCI-Express2.0(Gen2)5.0GT/s× 8 |

| Power supply | + 12 V ± 9% 3.57 A (45 W) |

| Operating environment | Temperature 0 to 50 ° C, humidity 35% to 85% (no condensation) |

| Size | 192.65 mm × 111.15 mm, panel width 20 mm (not including projections) |

| Weight | 232g |

| Supported OS | Windows 7/8 compatible with 32 bit / 64 bit |

| Environmental response | RoHS |

– The specifications and appearance stated are subject to change without notice.

– Power consumption does not include inrush current.

– In order to use the product correctly, be sure to read the instruction manual before using the product. Also, use the product under the conditions applicable to your product warranty.

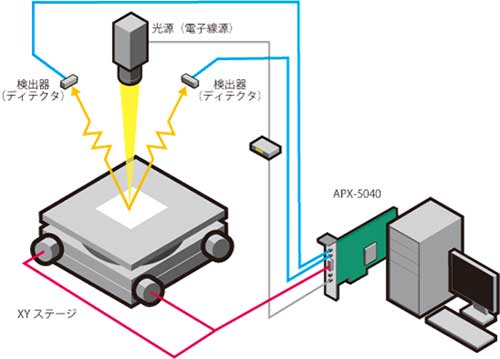

The figure shows an example of a system configuration that observes objects while controlling the low-speed XY stage.

Altera FPGAs on the APX-5040 have the following environments from development environment to simulation and in-system verification.

FPGA development environment

– Quartus II(Altera)

For the simulation environment, Mentor Graphics company’s following is higprepared.

– ModelSim Altera Edition (It can also be ModelSim PE / ModelSim SE)

– ModelSim Altera Starter Edition (free: limited use of 10,000 lines)

For in-system verification, Altera’s following is prepared.

– SignalTap II

It is an FPGA that can install various customer’s filtering conditions etc,

but please consult with us about this customization,

please send e-mail to: sales@aval-global.com

ENG

ENG KOR

KOR CHN

CHN JPN

JPN