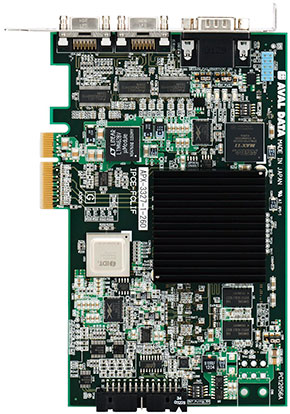

APX-3327-1-260

CL Base/Medium/Full/Deca x 1Ch, FPGA Board

| Model | APX-3327-1-260 |

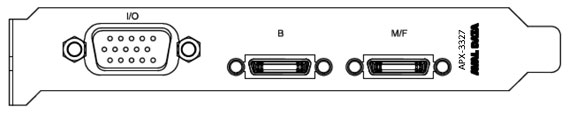

| Image input I / F | Camera Link Base / Medium / Full / Deca Configuration 1ch Two SDR 26 pin connectors installed Sampling clock 85 MHz (MAX) Area, line camera compatible |

| Memory | DDR 2 – SDRAM 512 MB (MEGA-FIFO: 128 MB, Work memory: 384 MB) |

| FPGA | ALTERA EP 2 AGX 260 (User-programmable image processing circuit by FPGA) |

| Sync output | Camera control signals: CC1 to CC4 General purpose output: 2 ch asynchronous, TTL / open collector (Available with the strobe timing output) |

| Sync input | External trigger: TTL / open collector / differential signal RS-422 Encoder: differential signal RS-422 (line driver), A / B / Z phase, 1 MHz (MAX) General purpose input: TTL / open collector |

| Event | Image input start, DMA end, GPIN etc. |

| System bus | PCI Express 2.0 x4 (Gen2) 5.0GT / S |

| Power | + 12V |

| Environment | Temperature : 0℃~50℃, humidity: 35% to 85% (no condensation) |

| Dimension | 167.65 mm x 111.15 mm, panel width 20 mm (without projections) |

| OS | Windows 10 / 7, (32bit / 64bit), Linux |

| Software (option) | SDK : AcapLib2, FPGA processing : AZP-FDK3327-01 |

Notes)

– The specifications and appearance stated are subject to change without notice.

– Power consumption does not include inrush current.

– In order to use the product correctly, be sure to read the instruction manual before using the product. Also, use the product under the conditions applicable to your product warranty.

– The specifications and appearance stated are subject to change without notice.

– Power consumption does not include inrush current.

– In order to use the product correctly, be sure to read the instruction manual before using the product. Also, use the product under the conditions applicable to your product warranty.

ENG

ENG KOR

KOR CHN

CHN JPN

JPN